## **Nanoscale**

PAPER

View Article Online

View Journal | View Issue

Cite this: Nanoscale, 2014, 6, 3830

# Poly-4-vinylphenol and poly(melamine-coformaldehyde)-based graphene passivation method for flexible, wearable and transparent electronics

In-yeal Lee,†<sup>a</sup> Hyung-Youl Park,†<sup>a</sup> Jin-hyung Park,<sup>a</sup> Gwangwe Yoo,<sup>a</sup> Myung-Hoon Lim,<sup>a</sup> Junsung Park,<sup>a</sup> Servin Rathi,<sup>a</sup> Woo-Shik Jung,<sup>b</sup> Jeehwan Kim,<sup>c</sup> Sang-Woo Kim,<sup>d</sup> Yonghan Roh,<sup>a</sup> Gil-Ho Kim\*<sup>a</sup> and Jin-Hong Park\*<sup>a</sup>

Next generation graphene-based electronics essentially need a dielectric layer with several requirements such as high flexibility, high transparency, and low process temperature. Here, we propose and investigate a flexible and transparent poly-4-vinylphenol and poly(melamine-co-formaldehyde) (PVP/PMF) insulating layer to achieve intrinsic graphene and an excellent gate dielectric layer at sub 200 °C. Chemical and electrical effects of PVP/PMF layer on graphene as well as its dielectric property are systematically investigated through various measurements by adjusting the ratio of PVP to PMF and annealing temperature. The optimized PVP/PMF insulating layer not only removes the native –OH functional groups which work as electron-withdrawing agents on graphene (Dirac point close to zero) but also shows an excellent dielectric property (low hysteresis voltage). Finally, a flexible, wearable, and transparent (95.8%) graphene transistor with Dirac point close to zero is demonstrated on polyethylene terephthalate (PET) substrate by exploiting PVP/PMF layer which can be scaled down to 20 nm.

Received 9th December 2013 Accepted 30th December 2013

DOI: 10.1039/c3nr06517k

www.rsc.org/nanoscale

## 1. Introduction

Next generation flexible, wearable, and transparent electronics (FWTEs) such as electronic-paper, wearable display, flexible touch screen, and transparent wall, are expected to be mechanically flexible, optically transparent, and light in weight.<sup>1-4</sup> For the transistors that these devices are fundamentally composed of, novel materials such as indium tin oxide (ITO), zinc tin oxide (ZTO), carbon nano tube (CNT), and polyimide have been previously proposed as electrode, active channel, and dielectric layers.<sup>5-10</sup> Although zero band gap graphene is limited in the present situation for complementary metal-oxide-semiconductor (CMOS) applications due to its low on/off-current ratio and high power consumption, it is still a promising candidate for FWTEs because of its high mobility (~200 000 cm² V s<sup>-1</sup>), flexibility (fracture strain of 30%), and

transparency (97.5% for monolayer). However, two critical issues need to be resolved before utilizing graphene as a FWTEs material; finding a flexible and transparent insulator for gate dielectric and maintaining its intrinsic electrical property.

Recently, 2D dielectrics such as boron nitride (BN) and mica have been applied for graphene-based devices because of low roughness, reduction of interfacial carrier scattering, and better scale-down potential for future devices.15 However, it is still a challenge to achieve large area BN and mica-based devices are incompatible with flexible electronics. Another insulating materials such as ion gel, high-k dielectric, and graphite oxide (GO) have been also studied for the graphene-based FWTEs. 16-19 Even though these insulators show good electrical combination with graphene, high cost of raw materials for ion gel, nonuniformity of the GO layer, and high thermal processing of high-k dielectric layer are hindering the successful integration of graphene-based FWTEs. In addition, it is a challenging task to achieve graphene layers with intrinsic property where the concentration of holes and electrons are symmetric. The root of these issues lies in the unexpected doping problem on graphene surface caused by native hydroxyl (-OH) functional groups under atmospheric ambient and polymer-residues deposited during the fabrication process.20-26 Because the p-type doping problem degrades the performance of graphene-based devices, several methods such as encapsulation by BN, vacuum anneal, and chemical cleaning process, have been proposed to remove

<sup>&</sup>quot;Samsung-SKKU Graphene Center, Sungkyunkwan Advanced Institute of Nanotechnology (SAINT) and School of Electronics and Electrical Engineering, Sungkyunkwan University, Suwon 440-746, Korea. E-mail: ghkim@skku.edu; jhpark9@skku.edu; Tel: +82-31-290-7970

<sup>&</sup>lt;sup>b</sup>Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA <sup>c</sup>IBM Thomas J. Watson Research Center, Yorktown Heights, New York 10598, USA <sup>d</sup>School of Advanced Materials Science and Engineering, SKKU Advanced Institute of Nanotechnology (SAINT), Center for Human Interface Nanotechnology (HINT), SKKU-Samsung Graphene Center, Sungkyunkwan University, Suwon 440-746, Korea † Equally contributed as the first author.

Paper

the unexpected -OH groups and polymer-residues on the graphene surface.<sup>27-29</sup> However, these methods are not suitable for FWTE technology because their processing temperature exceeds 200 °C where most flexible substrate is bound to melt and the interaction problem that exists between the chemical solution and the flexible substrate. Although a clean-lifting process through electrostatic generator which can provide a polymerresidue free graphene on flexible substrates has been reported recently,30 it does not seem to be free from the p-type doping problem by native -OH functional group formation. In this letter, we propose and investigate a poly-4-vinylphenol and poly(melamine-co-formaldehyde) (PVP/PMF)-based insulating layer to obtain a transparent and flexible gate dielectric layer on graphene and achieve and maintain intrinsic property of graphene at sub 200 °C. PVP/PMF-based insulator is a popular material for flexible and transparent organic electronics that can be easily formed by spinning-coating process and can also be scaled down by adjusting PVP/PMF concentration in PGMEA solution at sub 200 °C. In addition, the problematic -OH groups on native graphene can be effectively combined with PMF crosslinking agent while PVP/PMF insulator fabrication. Based on these findings, a flexible and transparent graphene-based transistor with Dirac point close to zero is fabricated to demonstrate the feasibility of PVP/PMF-based insulator on graphene-based FWTEs. Even though various polymer dielectrics, such as polyimide and PMMA, were previously used on graphene-based flexible devices,31,32 the surface passivation phenomenon by the dielectric on graphene has not been reported yet.

#### **Experimental details** 2.

### 2.1 Preparation of PVP/PMF solution

The 0.5 g of PVP was mixed with 4.5 g, 4.25 g, and 4 g of PGMEA to produce PVP solutions. Then, a different amount of PMF (0 g, 0.25 g, and 0.5 g) is added to these PVP solutions, yielding different PVP/PMF solutions which were respectively named as PVP/PMF 0%, 50%, and 100%.

### 2.2 Fabrication of graphene transistor

The graphene was synthesized on copper foil by conventional chemical vapor deposition (CVD) method.33 The graphene/Cu foil was etched in ferric chloride (FeCl<sub>3</sub>) and was transferred onto 300 nm thick silicon-dioxide (SiO2) on heavily n-doped Si substrate. The transferred graphene was patterned by optical lithography and oxygen (O<sub>2</sub>) plasma etching processes was used to define the active channel region of 8 μm of width and 80 μm of length. Finally, Ti (10 nm) and Au (50 nm) layers were deposited to form source/drain (S/D) metal electrodes by electron-beam evaporator.

## 2.3 Fabrication of PVP/PMF-based capacitor

The PVP/PMF 50% layer was spin-coated on p-type Si substrate, followed by 100 °C, 150 °C, and 200 °C anneal for 30 minutes to induce sufficient cross-linking process. Then, 100 nm thick Ni was deposited through a shadow metal mask with a square

pattern of 100 µm by 100 µm to form metal electrodes. Finally, metal (Ni)-insulator (PVP/PMF)-semiconductor (Si) structure based capacitor was fabricated.

## 2.4 Fabrication of transparent, flexible and wearable graphene electronics

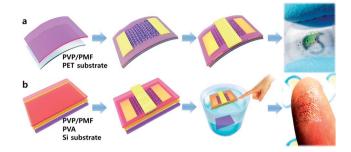

First of all, the bottom dielectric layer was spin-coated on polyethylene terephthalate (PET) substrate using the optimized PVP/PMF 50% solution, followed by curing process at 150 °C. After transferring graphene on PVP/PMF, we selectively deposited Ti/Au layers by a lift-off process to form S/D regions and then patterned an active graphene channel region. Then, the PVP/PMF layer was spin-coated and other patterned Ti/Au layers were deposited to make a gate stack. For wearable graphene device, graphene-PVP/PMF layers were first deposited on polyvinyl alcohol (PVA)/Si substrate and a top gate transistor fabrication process on the sample was performed. Finally, the fabricated transistor device was floated on deionized (DI) water to transfer onto arbitrary places (researcher's finger in this paper).

#### 3. Result and discussion

#### Raman spectroscopy analysis for PVP/PMF dielectric 3.1 layer

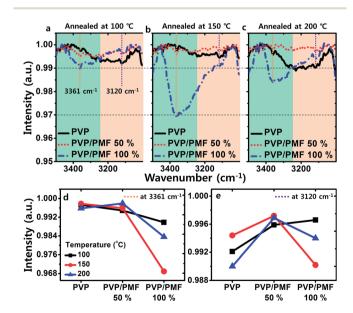

First, the chemical properties of PVP/PMF are investigated in order to study the cross-linking interaction between PVP and PMF. PVP/PMF solutions were spin-coated on n-type silicon (Si) substrates and were annealed at 100 °C, 150 °C, and 200 °C. Then, Fourier transform-infrared spectroscopy (FT-IR) measurement was performed on the samples to analyze -OH groups in the PVP/PMF layers. Fig. 1a-c show the spectra for

Fig. 1 Chemical analysis of PVP/PMF dielectric layers. FT-IR spectra of pure PVP, PVP/PMF 50%, and PVP/PMF 100% films annealed at (a) 100 °C, (b) 150 °C, and (c) 200 °C. Comparison of the extracted peak intensities for -OH groups at (d) 3361 cm<sup>-1</sup> and (e) 3120 cm<sup>-1</sup>.

Nanoscale Paper

-OH groups in PVP/PMF layers, which are typically located between 3000 cm<sup>-1</sup> and 3400 cm<sup>-1</sup>. In the pure PVP sample without PMF, we found that the peak for -OH groups was around 3000 cm<sup>-1</sup> to 3250 cm<sup>-1</sup>. However, other peaks relating to -OH groups in PVP/PMF 50% and PVP/PMF 100% samples were observed at 3250 cm<sup>-1</sup> to 3450 cm<sup>-1</sup>. The reason for the different peak positions is related to the cross-linking mechanism between PVP and PMF, which makes PVP molecules to bond with PMF through -OH and -OH bonding during the annealing process, thereby reducing the number of -OH groups in PVP. As a result, -OH groups in the pure PVP and PVP/PMF films are respectively in non-hydrogen and hydrogen bonding states.29 The difference of bonding states makes the peaks to be located at the slightly different positions. In the case of PVP/ PMF 50%, as shown in Fig. 1d and e, very low and stable peak intensities were observed at all annealing temperatures compared to the PVP/PMF 100% sample, indicating that a proper concentration of PMF was mixed to cross-link with the -OH groups in PVP. It is predicted that high and unstable intensities of PVP/PMF 100% sample is attributed to the remaining -OH groups of PMF remaining after the cross-linking process.

## 3.2 Electrical analysis for PVP/PMF dielectric deposited graphene transistor with different PMF concentration

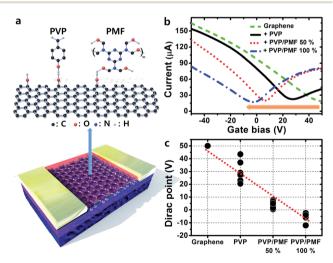

The PVP/PMF cross-linking process was then applied on the graphene surface by depositing and annealing PVP/PMF layers. Fig 2a shows the schematic diagram of the fabricated graphene transistor and possible chemical reactions among -OH groups in graphene, PVP, and PMF. As widely known, native -OH groups are easily formed on graphene surface under

Fig. 2 Schematic diagram for possible chemical interactions and carrier transporting properties of graphene devices passivated by PVP/ PMF with different PMF concentrations. (a) Schematic diagrams of fabricated graphene transistor, indicating chemical reactions by PVP and PMF on graphene. (b)  $I_D - V_G$  characteristics of graphene transistors exposed to air and encapsulated by pure PVP, PVP/PMF 50%, and PVP/ PMF 100% films (all of the samples were annealed at 200 °C). (c) Distribution of Dirac points extracted from the  $I_D$ - $V_G$  characteristics of 10 transistor samples for each annealing temperature

atmospheric condition, making the graphene layer to work as ptype materials.<sup>23</sup> Although there was an experimental report that the type of graphene converts to intrinsic through vacuum annealing process at 200 °C, very high positive Dirac point value  $(\sim 50 \text{ V})$  was still obtained in the graphene sample annealed at 200 °C meaning that the graphene is still strong p-type.<sup>28</sup> However, in the graphene transistors with PVP, PVP/PMF 50%, and PVP/PMF 100% layers, Dirac points were respectively shifted to 27 V, 6 V, and −2 V after the 200 °C anneal. It is thought that -OH groups in PVP and PVP/PMF are bonded with those on graphene surface during the annealing process, thus reducing the number of -OH groups on graphene. It seems that this effect is stronger as the PMF concentration increases in PVP solution. This observation suggests that the cross-linking process with -OH groups on graphene by PMF is expected to be more favorable than that by PVP at 200 °C. In order to re-verify the shifting of Dirac point according to different concentration of PMF, drain current-gate voltage  $(I_D-V_G)$  measurement and Dirac point extraction were performed on ten different graphene transistor devices, as shown in Fig. 2b and c. Here, it is confirmed that PVP/PMF layer can effectively reduce the number of -OH groups on graphene surface through the annealing process and PVP/PMF 50% is optimal in obtaining the intrinsic property of graphene with Dirac point at ~0 V and working properly as an insulating material. Higher concentration of PMF to PVP is also expected to cause slight n-type doping phenomenon (consequently, negative Dirac point) on graphene due to the triazine structure with N atoms in PMF.34

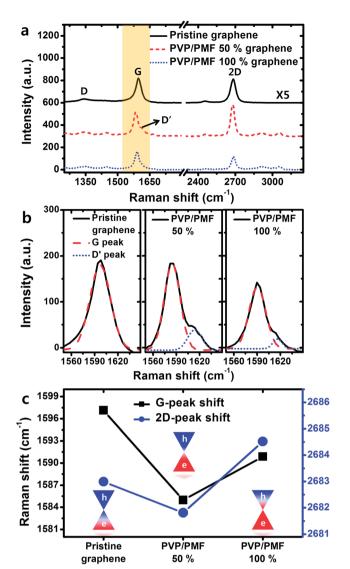

## 3.3 Raman analysis for graphene on PVP/PMF dielectric laver

Next, in order to investigate the change of graphene electronic structure according to the interaction between PVP/PMF and graphene, Raman spectroscopy ( $\lambda = 532$  nm) was performed on graphene layers transferred on various bottom films, such as SiO<sub>2</sub>, PVP/PMF 50%, and PVP/PMF 100%, which were annealed at 200 °C for 1 hour. Fig 3a shows the Raman spectra measured on the graphene layers, where we observed conventional graphene D-, G-, D', and 2D peaks at around  $1350 \text{ cm}^{-1}$ ,  $1590 \text{ cm}^{-1}$ , 1618 cm<sup>-1</sup>, and 2683 cm<sup>-1</sup>, respectively. As shown in Fig. 3b, D' peak appeared at 1618 cm<sup>-1</sup> near G peak only in the graphene layers passivated by PVP/PMF 50% and 100% films. The newly appeared D' peaks in graphene samples reacted with PVP/PMF 50% and 100% layers can be explained by graphene structure modification through cross-linked -OH bonding and N atom doping phenomena between graphene and PVP/PMF layers. Yung-Chang Lin et al. and Zhiqiang Luo et al. also observed the D' peak in doped graphene layers and explained that it is attributed to the structural change of graphene surface by doping process.35,36 In addition, the three graphene samples (pristine, PVP/PMF 50%, and PVP/PMF 100%) show different positions of G and 2D peaks in Fig. 3c. In the case of pristine graphene sample, its G peak appeared at around 1597 cm<sup>-1</sup> which is a slightly up-shifted value from that of intrinsic graphene ( $\sim$ 1584 cm<sup>-1</sup>), confirming its p-type property that was previously concluded by  $I_D$ - $V_G$  measurement. However, after

Fig. 3 (a) Raman spectra for pristine graphene on SiO<sub>2</sub> layer and graphene on PVP/PMF (50% and 100%) layers. (b) Lorentz fitting curves for G- and D'-peaks of the three graphene layers. (c) Raman shift of Gand 2D-peak positions in the three graphene layers.

depositing PVP/PMF 50% and 100% layers on graphene and annealing the samples, the G peaks were respectively shifted to  $\sim$ 1584 cm<sup>-1</sup> and  $\sim$ 1591 cm<sup>-1</sup>. It is thought that the crosslinking process between graphene and PVP/PMF 50% layer seems to make the sample more intrinsic, which is also supported by Dirac point close to zero shown in Fig. 2b and c. In PVP/PMF 100% with more PMF molecules, graphene layer is expected to be n-type doped again through reaction with PMF because of its G peak up-shifted to  $\sim$ 1591 cm<sup>-1</sup>. This is also observable as a negative Dirac point in the Fig. 2b and c. In previous reports, the position of G peak was observed to be upshifted in both of p- and n-type doped graphene layers.<sup>37</sup> The positions of 2D peaks in pristine and PVP/PMF 100% samples were observed at higher frequency ( $\sim 2685 \text{ cm}^{-1}$ ), compared to that ( $\sim$ 2680 cm<sup>-1</sup>) in PVP/PMF 50% sample, supporting the conclusion that p-type property of pristine graphene is changed

to n-type through intrinsic as using PVP/PMF layer with higher PMF concentration. Xiaochen Dong et al. also reported that 2D peaks were up-shifted when p- and n-type doping was performed on graphene.38

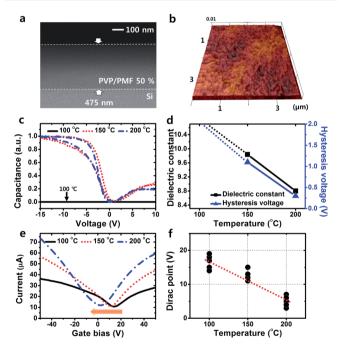

## 3.4 Capacitance-voltage analysis for PVP/PMF dielectric layer

Since the PVP/PMF layer needs to perform as a dielectric layer on the graphene-based devices, its dielectric properties (dielectric constant and hysteresis) are investigated through capacitance-voltage (C-V) analysis on metal-PVP/PMF-Si structure capacitors. For this experiment, PVP/PMF 50% layer was selected due to its proper chemical reaction with graphene providing Dirac point close to zero. The thickness of PVP/PMF 50% layer is 470 nm, showing quite uniform roughness with the root mean square (RMS) value of 8 nm, as shown in the scanning electron microscope (SEM) and atomic force microscope (AFM) images (Fig. 4a and b). The capacitance values were measured at 1 MHz between -15 V and 10 V, and the dielectric constants and extracted hysteresis window voltages were plotted as a function of the annealing temperature in Fig. 4c and d. Based on the C-V curves of the samples annealed at 150 °C and 200 °C which clearly show accumulation, depletion, and

Fig. 4 Dielectric properties of PVP/PMF and carrier transporting properties of graphene devices passivated by PVP/PMF achieved at different temperatures. (a) Cross sectional SEM image of capacitor with PVP/PMF 50% layer. (b) AFM image taken on the PVP/PMF 50% layer. (c) Normalized capacitance-voltage (C-V) characteristics as a function of the annealing temperature (100 °C, 150 °C, and 200 °C) of the capacitors with PVP/PMF 50% layer. (d) Dielectric constants and hysteresis voltages extracted from the C-V characteristics. (e)  $I_D-V_G$ characteristics of graphene transistors with PVP/PMF 50% layer, annealed at 100 °C, 150 °C, and 200 °C. (f) Distribution of Dirac points extracted from the  $I_D$ - $V_G$  characteristics of 10 transistor samples for each annealing temperature.

Nanoscale Paper

inversion regions, the PVP/PMF layer seems to work properly as a dielectric layer. However, in the sample annealed at 100 °C, dielectric behavior was not observed because of insufficient curing temperature to trigger the cross-linking process of PVP and PMF. The cross-linking process is generally known to be induced actively above 151 °C, which is the glass transition temperature of PVP.39 Especially, compared to the previously reported dielectric constant ( $\sim$ 4) of PVP/PMF, relatively higher dielectric constant (8-10) was observed in this 470 nm thick PVP/PMF layer because non-cured -OH groups in the PVP/PMF worked as moisture absorbers at the surface of PVP film.40 In addition, as the annealing temperature increases, the dielectric constant and hysteresis window values are decreased. It is predicted that this is related to the -OH groups in PVP/PMF layer working as charge traps. The number of -OH groups seems to be reduced through the cross-linking process at higher curing temperature. It consequently minimizes the chargetrapping effect and decreases the hysteresis window value by achieving higher charge density on the PVP/PMF-Si interface. Besides, since the lack of -OH groups means that surface of the PVP/PMF layer is more hydrophobic, water diffusion into the higher temperature annealed PVP/PMF layer seems difficult and the probability of dielectric constant decrease through the diffused moisture is consequently expected to be high.

# 3.5 Electrical analysis for PVP/PMF dielectric deposited graphene transistor with different curing temperature

The effect of curing process temperature for PVP/PMF layer on graphene surface is also investigated by placing emphasis on the Dirac point of transistors fabricated on the graphene samples. PVP/PMF 50% layer was deposited on graphene transistors and the samples were annealed at 100 °C, 150 °C, and 200 °C for 30 minutes. As shown in Fig. 4e and f, the Dirac point was shifted from 16 V to 3 V with the increase of annealing temperature. It is thought that the higher annealing temperature enables more number of -OH groups in PVP/PMF to be cross-linked with those on graphene surface. As a result, PMF molecules bonded with the native -OH groups on graphene are expected to induce negative shift of Dirac point and improve hole and electron conduction. Although the curing process at 200 °C makes the PVP/PMF layer to behave as a better dielectric material and also achieve the most intrinsic graphene property, 150 °C process was selected in this work by considering the applications on flexible substrates such as PET, polyimide (PI), etc., which typically have a fairly low melting point around 150 °C to 250 °C.

# 3.6 Application devices: transparent, flexible and wearable graphene electronics

In order to demonstrate the advantages of PVP/PMF, graphene-based FWTEs on PET substrate were fabricated by using PVP/PMF and graphene as dielectric and channel layers (Fig. 5a) respectively. Moreover, the graphene FWTE device was successfully transferred onto a researcher's finger, as shown in Fig. 5b, showing the feasibility of the device to future wearable electronic applications. The  $I_{\rm D}$ – $V_{\rm G}$  measurement was carried out

Fig. 5 Fabrication process flows for (a) flexible electronics on PET and (b) wearable electronics on a finger.

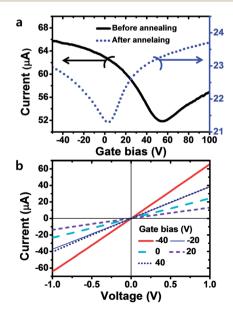

by sweeping  $V_{\rm G}$  from -50 V to 100 V at  $V_{\rm DS}=1$  V in the PVP/PMF 50% graphene FWTEs. Although the conventional V-shape  $I_{\rm D}$ – $V_{\rm G}$  characteristic was obtained (dark line) as shown in Fig. 6a, its Dirac point was around 55 V indicating that graphene works as p-type material. This large positive shift of Dirac point can be explained by re-generation of –OH groups while forming the top gate stack. In order to recover the Dirac point through the cross-linking process between –OH groups of graphene and PVP/PMF layers, the devices were annealed again at  $150\,^{\circ}$ C for 10 minutes and consequently the Dirac point moved back to about 1 V (blue line). In spite of the chemical reaction on graphene surface, like conventional graphene transistor devices,  $I_{\rm D}$  is still linearly dependent on  $V_{\rm D}$  and also modulated by  $V_{\rm G}$ , as shown in Fig. 6b.

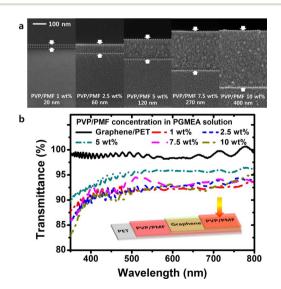

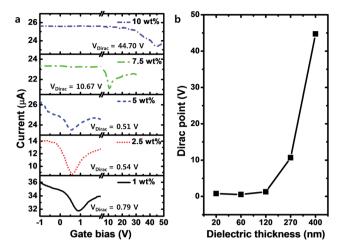

Although the top gated graphene transistor was successfully demonstrated with PVP/PMF 50% gate dielectric layer (470 nm thick), it requires high operating gate voltage and consequently makes it difficult to fabricate high performance FWTEs. Thus, we additionally scaled the thickness of PVP/PMF dielectric layer by adjusting PVP/PMF concentration in the PGMEA solution

**Fig. 6** Carrier transporting properties of graphene-based FWTEs. (a)  $I_{\rm D}-V_{\rm G}$  and (b)  $I_{\rm D}-V_{\rm D}$  characteristics for the graphene-based flexible transistor.

(1 wt% to 10 wt%) and investigated the transmittance/Dirac points. Fig. 7a shows SEM cross-sectional images for the scaled PVP/PMF dielectric layers (scaled from  $\sim$ 400 nm to  $\sim$ 20 nm). For estimating quantitative reduction in transmittance value owing to the additional PVP/PMF layers, ultraviolet-visible-near infrared absorption spectroscopy (UV-VIS-NIR) analysis was performed in the 300-800 nm regime and a reference graphene sample was compared with PVP/PMF 50% layer samples, as shown in Fig. 7b. The transmittance values measured at 550 nm wavelength on the (PVP/PMF) + graphene + (PVP/PMF) + PET samples are respectively 92%, 93%, 96%, 94%, and 92% for the cases of 1 wt%, 2.5 wt%, 5 wt%, 7.5 wt%, and 10 wt% PVP/PMF concentrations, indicating that the transparency of the graphene FWTEs is relatively higher than that of present FWTEs using ion gel dielectric, high-K dielectric, GO, and CNT.41-43 Especially, the highest transmittance value of ~96% was observed in the case of 5 wt% PVP/PMF concentration in PGMEA. It is thought that the scaled film thickness and the refractive index changed by dielectric constant caused the variation of transmittance values since the reduction of dielectric constants was observed as the thickness of PVP/PMF layers was scaled down.40 Then, in order to investigate the scaling effect of PVP/PMF dielectric thickness on the electrical properties of graphene transistors with PVP/PMF gate dielectric,  $I_D$ - $V_G$ characteristics were measured on the device samples (Fig. 8a) and the extracted Dirac points were plotted as a function of dielectric thickness in Fig. 8b. As the dielectric thickness was scaled down from 400 nm to 20 nm, Dirac point showed a decreasing tendency from 44.7 V to 0.79 V and a practical low operating gate voltage (~2 V) was also obtained below 120 nm thick dielectric samples. It is thought that a gate control is successfully improved through the reduction of PVP/PMF

Fig. 7 Thickness and transmittance properties of the scaled PVP/PMF dielectrics. (a) SEM cross-sectional images of PVP/PMF dielectric layers respectively formed by 1 wt%, 2.5 wt%, 5 wt%, 7.5 wt%, and 10 wt% PVP/PMF solutions. (b) Transmittance spectra measured on the (PVP/ PMF) + graphene + (PVP/PMF) + PET samples (Inset: structure) with different thickness of the PVP/PMF layer.

Fig. 8 Carrier transporting properties of graphene-based FWTEs according to PVP/PMF dielectric thickness. (a)  $I_{\rm D}$ - $V_{\rm G}$  characteristics and (b) Dirac points as a function of the thickness of the PVP/PMF laver.

dielectric thickness, consequently demonstrating the feasibility of PVP/PMF dielectric-based graphene FWTEs.

## Conclusion

In conclusion, PVP/PMF-based insulating layers for graphenebased FWTEs were proposed and investigated to obtain transparent and flexible gate dielectric layer and achieve an intrinsic property of graphene at sub 200 °C. The optimum conditions for fabricating graphene FWTEs using PVP/PMF insulating layer were determined as 50% PMF in PVP and 150 °C anneal through FT-IR, I-V, Raman, and C-V analyses. Finally, flexible, wearable, and transparent graphene devices were demonstrated with Dirac point close to zero using the PVP/PMF 50% layer on PET substrate and transferring it to a researcher's finger. Moreover, the PVP/PMF 50% layer was successfully scaled from 400 nm down to 20 nm by adjusting PVP/PMF concentration in PGMEA solution, consequently resulting in the reduction of operating gate voltage ( $\sim$ 100 V to  $\sim$ 2 V). The transparency of graphene FWTEs showed very high values of above 92% (especially,  $\sim$ 96% in the case of 5 wt% PVP/PMF concentration in PGMEA), which are relatively higher than that of present FWTEs. Therefore, we expect that the highly transparent, scalable, and flexible PVP/ PMF layers can be used for dielectric and surface passivation materials in future graphene-based FWTE devices.

## Acknowledgements

This work was supported by Basic Science Research Programs through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (NRF-2011-0007997 and 2012R1A1A2042230).

## References

1 J. U. Park, S. Nam, M. S. Lee and C. M. Lieber, Nat. Mater., 2011, 11, 120-125.

Nanoscale Paper

- 2 S. Sanvito, Nat. Mater., 2007, 6, 803-804.

- 3 S. Bae, H. Kim, Y. Lee, X. Xu, J. S. Park, Y. Zheng, J. Balakrishana, T. Lei, H. R. Kim, Y. I. Song, Y. J. Kim, K. S. Kim, B. Ozyilmaz, J. H. Ahn, B. H. Hong and S. Iijima, *Nat. Nanotechnol.*, 2010, 5, 574–578.

- 4 G. Eda, G. Fanchini and M. Chhowalla, *Nat. Nanotechnol.*, 2008, 3, 270-274.

- 5 S. I. Na, S. S. Kim, J. Jo and D. Y. Kim, *Adv. Mater.*, 2008, **20**, 4061–4067.

- 6 J. Huang, X. Wang, Y. Kim, A. J. deMello, D. D. C. Bradley and J. C. deMello, *Phys. Chem. Chem. Phys.*, 2006, 8, 3904–3908.

- 7 W. B. Jackson, R. L. Hoffman and G. S. Herman, *Appl. Phys. Lett.*, 2005, 87, 193503.

- 8 N. Chimot, V. Derycke, M. F. Goffman, J. P. Bourgoin and H. Happy, *Appl. Phys. Lett.*, 2007, **91**, 153111.

- 9 A. Nadarajah, R. C. Word, J. Meiss and R. Knenkamp, *Nano Lett.*, 2007, 8, 534–537.

- 10 D. J. Liaw and F. C. Chang, J. Polym. Sci., Part A: Polym. Chem., 2002, 40, 5766-5774.

- 11 N. Petrone, C. R. Dean, I. Meric, A. M. van der Zande, P. Y. Huang, L. Wang, D. Muller, K. L. Shepard and J. Hone, *Nano Lett.*, 2012, 12, 2751–2756.

- 12 C. Lee, X. Wei, J. W. Kysar and J. Hone, *Science*, 2008, **321**, 385–388.

- 13 L. G. De Arco, Y. Zhang, C. W. Schlenker, K. Ryu, M. E. Thompson and C. Zhou, ACS Nano, 2010, 4, 2865–2873.

- 14 K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J. H. Ahn, P. Kim, J. Y. Choi and B. H. Hong, *Nature*, 2009, 457, 706–710.

- 15 J. Shim, C. H. Lui, T. Y. Ko, Y. J. Yu, P. Kim, T. F. Heinz and S. Ryu, *Nano Lett.*, 2012, **12**, 648–654.

- 16 S. M. Kim, E. B. Song, S. Lee, J. Zhu, D. H. Seo, M. Mecklenburg, S. Seo and K. L. Wang, ACS Nano, 2012, 6, 7879–7884.

- 17 B. Standley, A. Mendez, E. Schmidgall and M. Bockrath, *Nano Lett.*, 2012, **12**, 1165–1169.

- 18 S. K. Lee, H. Y. Jang, S. Jang, E. Choi, B. H. Hong, J. Lee, S. Park and J. H. Ahn, *Nano Lett.*, 2012, 12, 3472–3476.

- 19 B. J. Kim, H. Jang, S. K. Lee, B. H. Hong, J. H. Ahn and J. H. Cho, *Nano Lett.*, 2010, **10**, 3464–3466.

- 20 D. W. Shin, H. M. Lee, S. M. Yu, K. S. Lim, J. H. Jung, M. K. Kim, S. W. Kim, J. H. Han, R. S. Ruoff and J. B. Yoo, ACS Nano, 2012, 6, 7781–7788.

- 21 Z. Cheng, Q. Zhou, C. Wang, Q. Li, C. Wang and Y. Fang, *Nano Lett.*, 2011, **11**, 767–771.

- 22 A. G. F. Garcia, M. Neumann, F. Amet, J. R. Williams, K. Watanabe, T. Taniguchi and D. Goldhaber-Gordon, *Nano Lett.*, 2012, 12, 4449–4454.

- 23 H. Sojoudi, J. Baltazar, C. Henderson and S. Graham, *J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.*, 2012, **30**, 041213.

- 24 A. Lopez-Bezanilla, F. Triozon and S. Roche, *Nano Lett.*, 2009, 9, 2537–2541.

- 25 C. Mattevi, F. Colleaux, H. Kim, Y. H. Lin, K. T. Park, M. Chhowalla and T. D. Anthopoulos, *Nanotechnology*, 2012, 23, 344017.

- 26 W. C. Shin, S. Seo and B. J. Cho, Appl. Phys. Lett., 2011, 98, 153505.

- 27 A. S. Mayorov, R. V. Gorbachev, S. V. Morozov, L. Britnell, R. Jalil, L. A. Ponomarenko, P. Blake, K. S. Novoselov, K. Watanabe, T. Taniguchi and A. K. Geim, *Nano Lett.*, 2011, 11, 2396–2399.

- 28 L. Jiao, L. Zhang, X. Wang, G. Diankov and H. Dai, *Nature*, 2009, 458, 877–880.

- 29 H. Kim, D. Kim, J. Lee, H. So, J. Lee, B. Kim and M. Hong, *Org. Electron.*, 2011, **12**, 1043–1047.

- 30 D. Y. Wang, I. S. Huang, P. H. Ho, S. S. Li, Y. C. Yeh, D. W. Wang, W. L. Chen, Y. Y. Lee, Y. M. Chang, C. C. Chen, C. T. Liang and C. W. Chen, Adv. Mater., 2013, 25, 4521.

- 31 J. Lee, L. Tao, Y. Hao, R. S. Ruoff and D. Akinwande, *Appl. Phys. Lett.*, 2012, **100**, 152104.

- 32 J. H. Choi, G. H. Lee, S. Park, D. Jeong, J. O. Lee, H.-S. Sim, Y. J. Doh and H. J. Lee, *Nat. Commun.*, 2013, **4**, 2525.

- 33 K. H. Lee, H. J. Shin, J. Lee, I. Y. Lee, G. H. Kim, J. Y. Choi and S. W. Kim, *Nano Lett.*, 2012, **12**, 714–718.

- 34 F. Y. Yang, K. J. Chang, M. Y. Hsu and C. C. Liu, *J. Mater. Chem.*, 2008, **18**, 5927–5932.

- 35 Y. C. Lin, C. Y. Lin and P. W. Chiu, Appl. Phys. Lett., 2010, 96, 133110.

- 36 Z. Luo, S. Lim, Z. Tian, J. Shang, L. Lai, B. MacDonald, C. Fu, Z. Shen, T. Yu and J. Lin, *J. Mater. Chem.*, 2011, 21, 8038–8044.

- 37 A. Das, S. Pisana, B. Chakraborty, S. Piscanec, S. K. Saha, U. V. Waghmare, K. S. Novoselov, H. R. Krishnamurthy, A. K. Geim, A. C. Ferrari and A. K. Sood, *Nat. Nanotechnol.*, 2008, 3, 210–215.

- 38 X. Dong, D. Fu, W. Fang, Y. Shi, P. Chen and L. J. Li, *Small*, 2009, 5, 1422–1426.

- 39 D. K. Hwang, J. H. Park, J. Lee, J. M. Choi, J. H. Kim, E. Kim and S. Im, *J. Electrochem. Soc.*, 2006, **153**, G23–G26.

- 40 S. H. Kim, S. Nam, J. Jang, K. Hong, C. Yang, D. S. Chung, C. E. Park and W. S. Choi, *J. Appl. Phys.*, 2009, **105**, 104509.

- 41 S. K. Lee, H. Y. Jang, S. Jang, E. Choi, B. H. Hong, J. Lee, S. Park and J. H. Ahn, *Nano Lett.*, 2012, **12**, 3472–3476.

- 42 D. T. Jiang, D. M. Hulbert, U. Anselmi-Tamburini, T. Ng, D. Land and A. K. Muherjee, J. Am. Ceram. Soc., 2007, 91, 151–154.

- 43 S. K. Lee, B. J. Kim, H. Jang, S. C. Yoon, C. Lee, B. H. Hong, J. A. Rogers, J. H. Cho and J. H. Ahn, *Nano Lett.*, 2011, 11, 4642–4646.